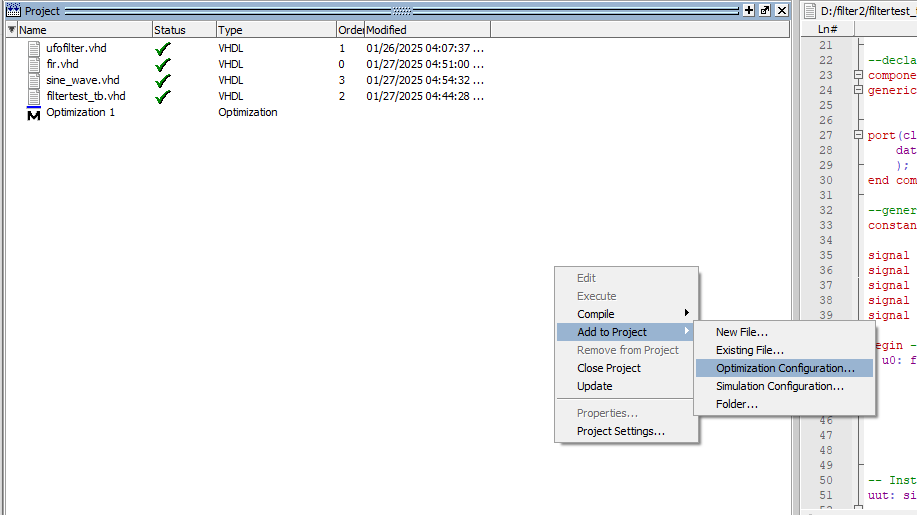

Project window에서 mouse right click

필요한 파일을 모두 추가한다.

내부변수 확인을 위해 다음에 ckeck하고 저장한다.

compile 정상적으로 끝나면 아래와 같이 표시된다.

optimization을 double click하면 simulation이 시작된다.

objedt window에서 출력하고자하는 변수를 wave window로 추가한다.

완료되면 ctrl-s를 눌러 저장한다.

저장한 파일이 있으면 do wave.do를 이용하여 불러오기를 한다.

run 10000 명령을 이용하여 simulation을 실행한다.

graph로 표시하고 싶은 변수는 format/alalog를 이용하여 표시한다.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.numeric_std.all;

use IEEE.STD_LOGIC_ARITH.ALL;

entity testbench is

--Port ();

end testbench;

architecture behave of testbench is ------------------------

component ufo_encoder port (

clk : in std_logic;

clr_n : in std_logic;

a_phase, b_phase : in std_logic;

rd_data : out std_logic_vector (31 downto 0));

end component;

signal rd_data : std_logic_vector(31 downto 0);

signal clk, clr_n, a_phase, b_phase, rdn : std_logic;

begin

u0 : ufo_encoder port map(

clk => clk,

clr_n => clr_n,

a_phase => a_phase,

b_phase => b_phase,

rd_data => rd_data

);

process

begin

clr_n <= '0';

wait for 1us;

clr_n <= '1';

wait;

end process;

process

begin

while true loop

clk <= '0';

wait for 5ns;

clk <= '1';

wait for 5ns;

end loop;

end process;

process

begin

b_phase <= '0';

while true loop

a_phase <= '0';

wait for 500ns;

b_phase <= '1';

wait for 500ns;

a_phase <= '1';

wait for 500ns;

b_phase <= '0';

wait for 500ns;

end loop;

end process;

end behave;

'FPGA' 카테고리의 다른 글

| nios menu (0) | 2021.10.01 |

|---|---|

| uncontrainsted signal (0) | 2021.09.26 |

| HLS + microblaze (0) | 2021.05.28 |

| vivado debugging (0) | 2020.06.14 |

| xilinx microblaze design (0) | 2020.04.22 |